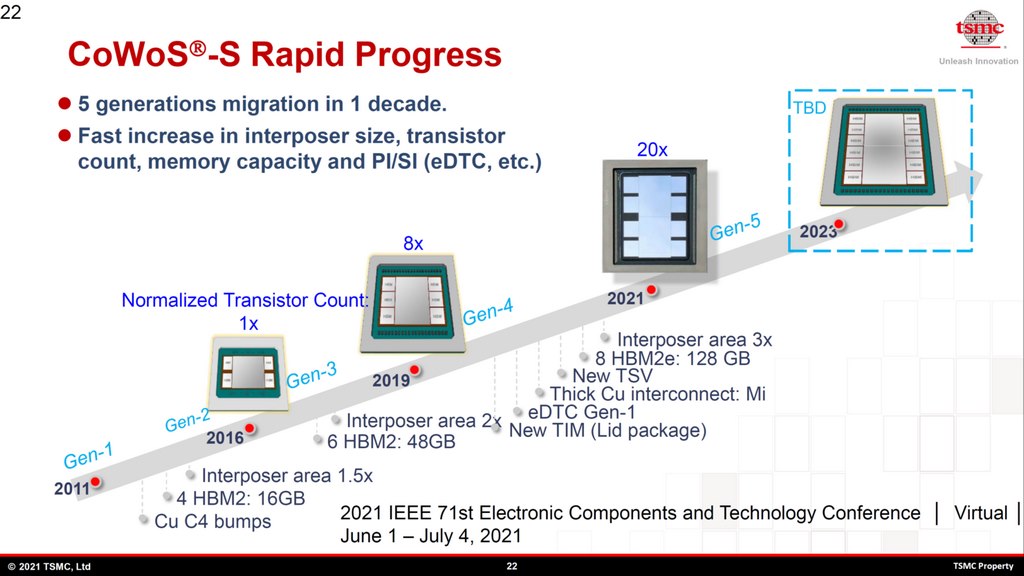

TSMC، تراشه ساز بزرگ تایوانی از برنامه خود برای بسته بندی فوق پیشرفته تراشههای نسل بعد رونمایی کرده که راهکار CoWos را که آمادگی پذیرایی معماریهای چیپلت و حافظه نسل آینده میباشد به نمایش گذاشته است. در سالهای اخیر رشد و پیشرفت TSMC در صنعت تراشه خیره کننده بوده و طی یک دهه این کمپانی موفق به عرضه 5 نسل مختلف از فناوری CoWos (Chip-on-Wafer-on-Substrate) شده که برخی از آنها در حال حاضر و برخی دیگر در فضای سرور و بازار مصرف کنندگان قرار خواهند گرفت. نقشه راه TSMC برای آینده حکایت از فناوریهای جدید و پیشرفتهای قابل توجه دارد.

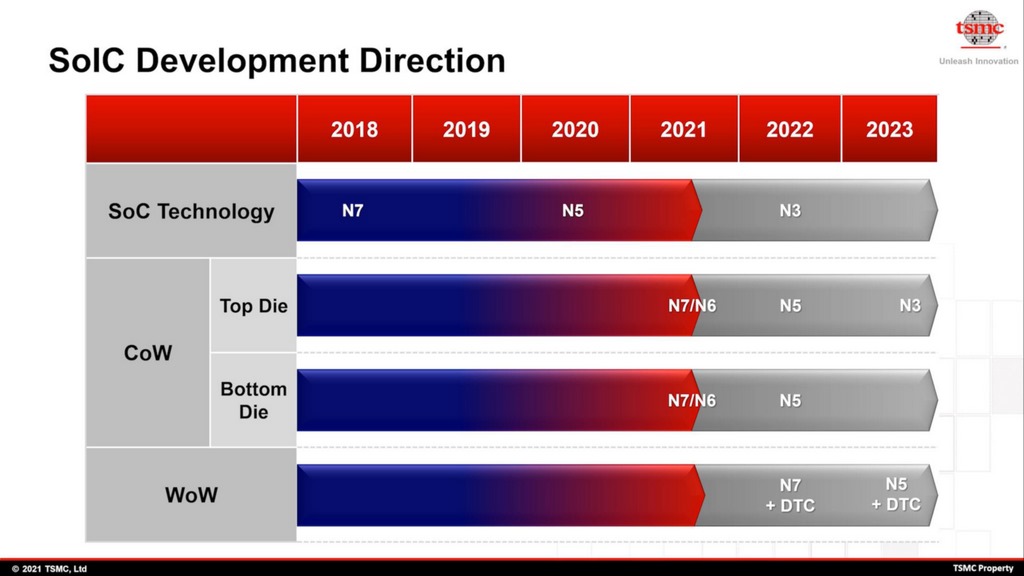

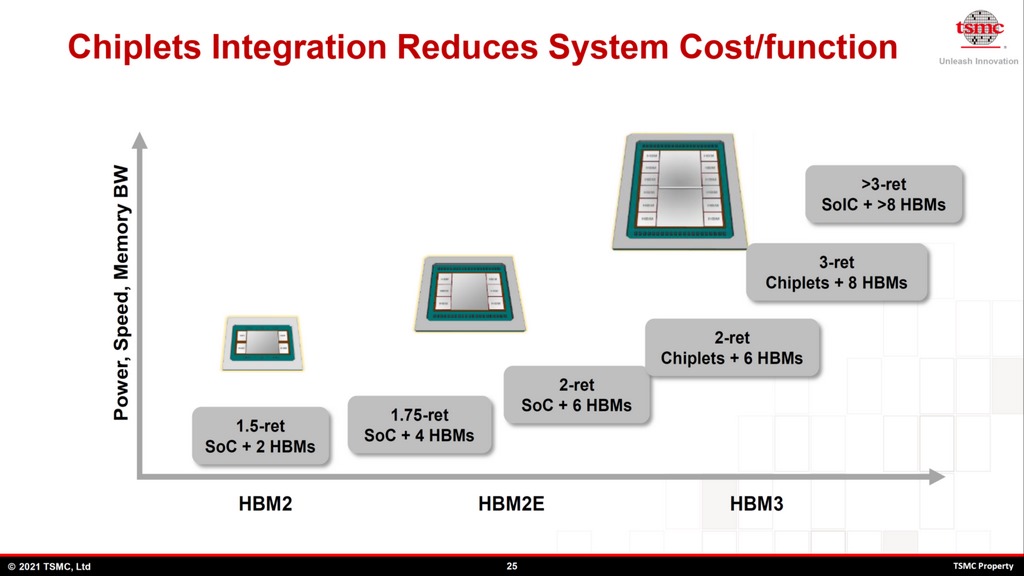

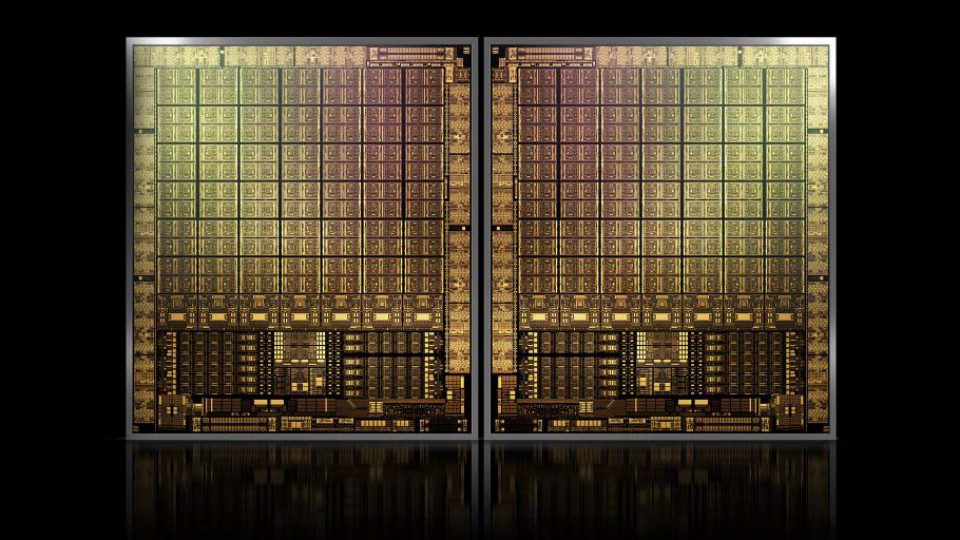

TSMC قصد دارد نسل پنجم راهکار بسته بندی CoWos خود را در ادامه سال جاری عرضه کند. نسل جدید در مقایسه با نسل سوم این فناوری 20 برابر ترانزیستورهای بیشتری را در خود جای میدهد که پیشرفت قابل ملاحظهای است. سطح واسطه در بسته بندی نسل جدید TSMC تا سه برابر افزایش یافته و قابلیت پشتیبانی از 8 حافظه HBM2e با حداکثر ظرفیت 128 گیگابایت را داراست. از دیگر ویژگیهای نسل بعدی راهکار CoWos می توانیم به راهکار جدید TSV، ارتباط متقابل Thick CU و همچنین یک TIM جدید (Lid package) اشاره کرد. اما مهمترین روشی که از نسل پنجم فناوری بسته بندی تراشه TSMC استفاده خواهد شد، پردازندههای گرافیکی MI200 کمپانی AMD با اسم رمز Aldebaran است.

- سفارشات عظیم اینتل برای فناوری 3 نانومتری TSMC – تاکتیک (کثیف) غول آبی

- تاخیر در ساخت کارخانه نیمههادی TSMC ایالات متحده

نقشه راه TSMC و آمادگی تولید گرافیک های نسل بعد انویدیا و AMD

گرافیکهای Aldebaran تیم قرمز اولین سری از گرافیکهای MCM GPU خواهد بود که توسط کمپانی TSMC به تولید خواهد رسید. این پردازشگرهای گرافیکی بر پایه معماری AMD CDNA 2 توسعه داده شدهاند و مشخصات فنی شایعه شده در مورد آنها مانند برخورداری از بیش از 16 هزار هسته و 128 گیگابایت حافظه HBM2E فوق العاده به نظر میرسد. احتمال استفاده از این فناوری در گرافیکهای Hopper انویدیا نیز وجود دارد که از معماری چیپلت MCM برخوردار خواهند بود و تولید این محصولات نیز بر عهده TSMC است. این گرافیک در سال 2022 روانه بازار خواهد شد و می توانیم انتظار داشته باشیم که انویدیا نیز از نسل پنجم راهکار بسته بندی TSMC استفاده کند.

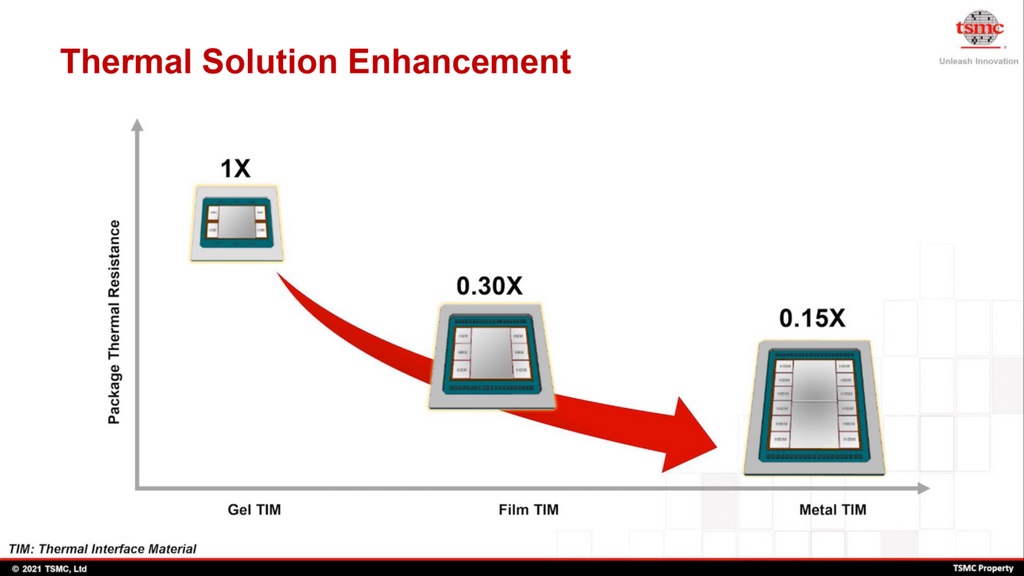

اگر چه نسل پنجم راهکار بسته بندی تراشه TSMC عرضه نشده اما در مورد نسل ششم این فناوری گفته میشود که تراشه ساز تایوانی در نسل بعد سطح بزرگ ترین برای یکپارچه سازی چیپلتهای بیشتر در اختیار خواهد داشت. طراحی این بسته بندی هنوز از سوی TSMC نهایی نشده اما انتظار میرود که تا 8 تراشه حافظه HBM2E و دو واحد پردازشی بر روی همان سطح قرار بگیرند. همچنین TSMC به دنبال عرضه راهکار حرارتی جدیدی در فرم Metal Tim است که انتظار میرود در مقایسه با همین راهکار در نسل، مقاومت حرارتی را به 0.15 کاهش دهد. هر چند این فناوری برای محصولاتی که در آینده با فناوری ساخت N3 به تولید خواهند رسید استفاده میشود.

دیدگاهتان را بنویسید