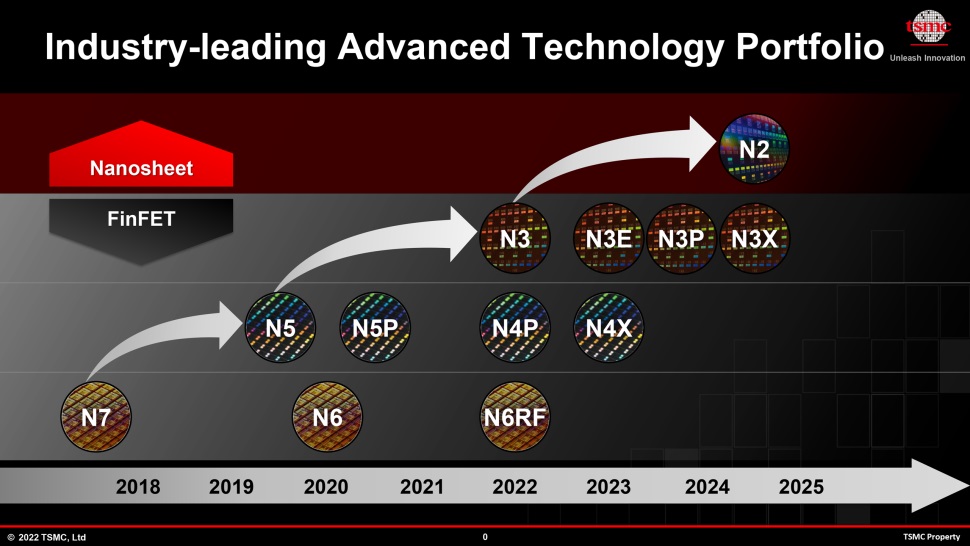

TSMC امروز به صورت رسمی از تکنولوژی ساخت 2 نانومتری N2 خود رونمایی کرد و همچنین تایید کرد که در این نوع تراشه ها از ترانزیستورهای GAAFETs استفاده خواهد شد. تکنولوژی ساخت جدید این کمپانی دو نوآوری اساسی به ارمغان خواهد آورد. ترانزیستورهای Nanosheet و backside power rail که هر دوی اینها برای افزایش پرفورمنس در هر وات بر روی نود در نظر گرفته شدهاند.

ترانزیستورهای نانوصفحهای (Nanosheet) دارای کانالهای چهارطرفه هستند که از هر چهار طرف توسط gate احاطه شدهاند و این نشت جریان را کاهش میدهد. علاوه بر اینها کانالها را میتوان عریضتر کرد تا با افزایش Drive Current پرفورمنس را ارتقا دهد و مصرف برق را نیز کاهش خواهد داد.

برای تغذیه ترانزیستورهای Nanosheet با توان کافی و هدر ندادن جریان، TSMC از روش backside power delivery استفاده میکند و این شرکت معتقد است که استفاده از این روش یکی از بهترین راه حلها برای حل مشکلات مربوط به جریان مقاومت در مرحله Back end of line ساخت IC است.

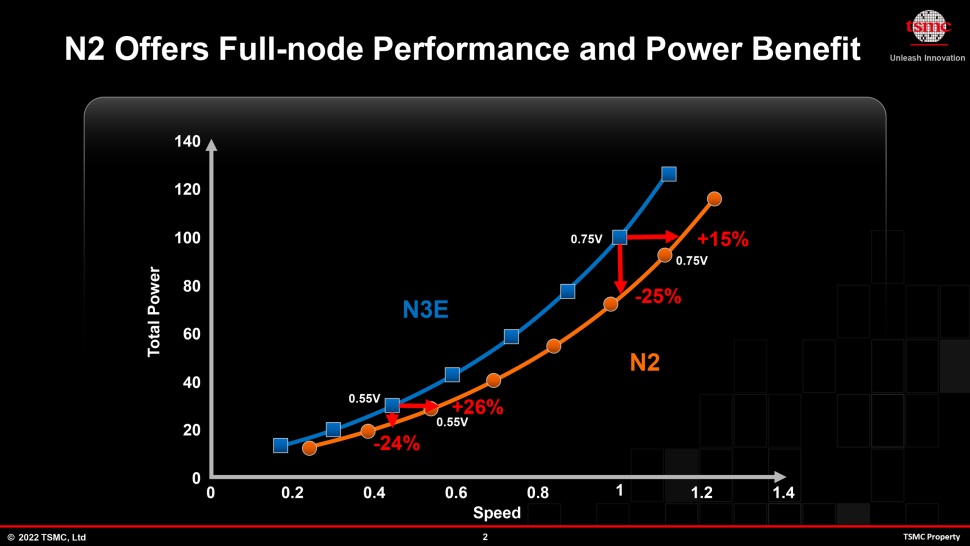

در واقع وقتی صحبت از عملکرد و مصرف انرژی به میان میآید، نودهای نانوشیت 2 نانومتری TSMC میتوانند پرفورمنس را تا 15 درصد ارتقا دهند و در عین حال میتوانند مصرف برق را تا حداکثر 30 درصد در همان فرکانس ترانزیستورهای محصولات 3 نانومتری کاهش دهند. با این حال تراکم چیپ در نودهای جدید در مقایسه با فناوری ساخت N3E تنها 1.1X است.

در مجموع نودهای 3 نانومتری TSMC افزایش عملکرد و کاهش مصرف را ارائه میکنند اما از نظر چگالی، فناوری 2 نانومتری به سختی میتواند علاقهمندان را تحت تاثیر قرار دهد. تراکم چیپ در واقع به تعداد ترانزیستورها در مساحت اشاره دارد.

همزمان با رونمایی رسمی از تکنولوژی ساخت 2 نانومتری TSMC و علاوه بر استفاده از ترانزیستورهای GAA nanosheet و تکنولوژی ارائه انرژی جدید، این کمپانی بستهبندی تراشه را به صورت ترکیبی درخواهد آورد و این کار علاوه بر بهینهسازی عملکرد، هزینهها را نیز کاهش خواهد داد. TSMC تکنولوژی ساخت جدید را برای عرضه در سال 2025 در نظر گرفته بنابراین انتظار میرود که در اواخر 2025 یا اوایل 2026 تراشههایی با این فناوری جدید در دسترس قرار گیرد.

دیدگاهتان را بنویسید