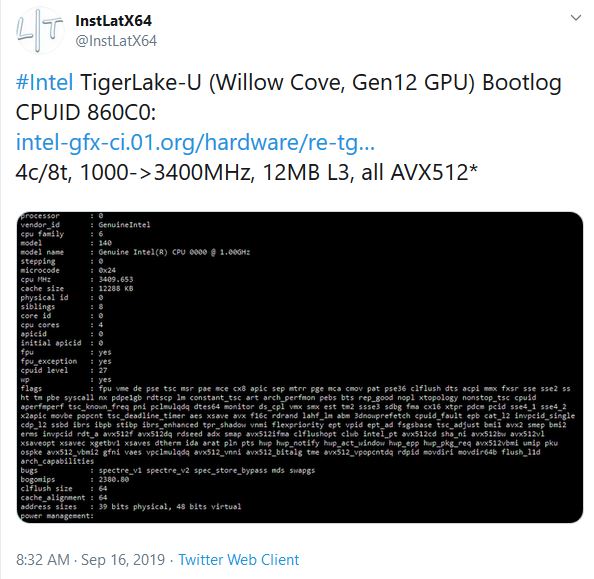

Tiger Lake U شامل 50 درصد حافظه کش سطح سه بیشتری خواهد بود، از 8 مگابایت به 12 مگابایت. این یعنی به ازای هر هسته 3 مگابایت حافظه کش سطح سه وجود خواهد داشت. همانطور که انتظار میرفت Tiger Lake U یک مدل چهار هسته با فناوری Hyper Threading خواهد بود. عکس پست شده همچنین نشان میدهد که نمونه مهندسی در فرکانس 3.4 گیگاهرتز فعالیت میکند که برای یک مدل اولیه، خوب ارزیابی میشود.

عکس همچنین شامل دستورالعملهای پشتیبانی شده در این معماری میباشد. تایید میکند که AVX 512 مانند Sunny Cove پشتیبانی خواهد شد اما به نظر نمیرسد avx512_bf باشد که برای پشتیبانی از bfloat16 نیاز است، چیزی که پردازندههای Cooper Lake Xeon به همراه دارند.

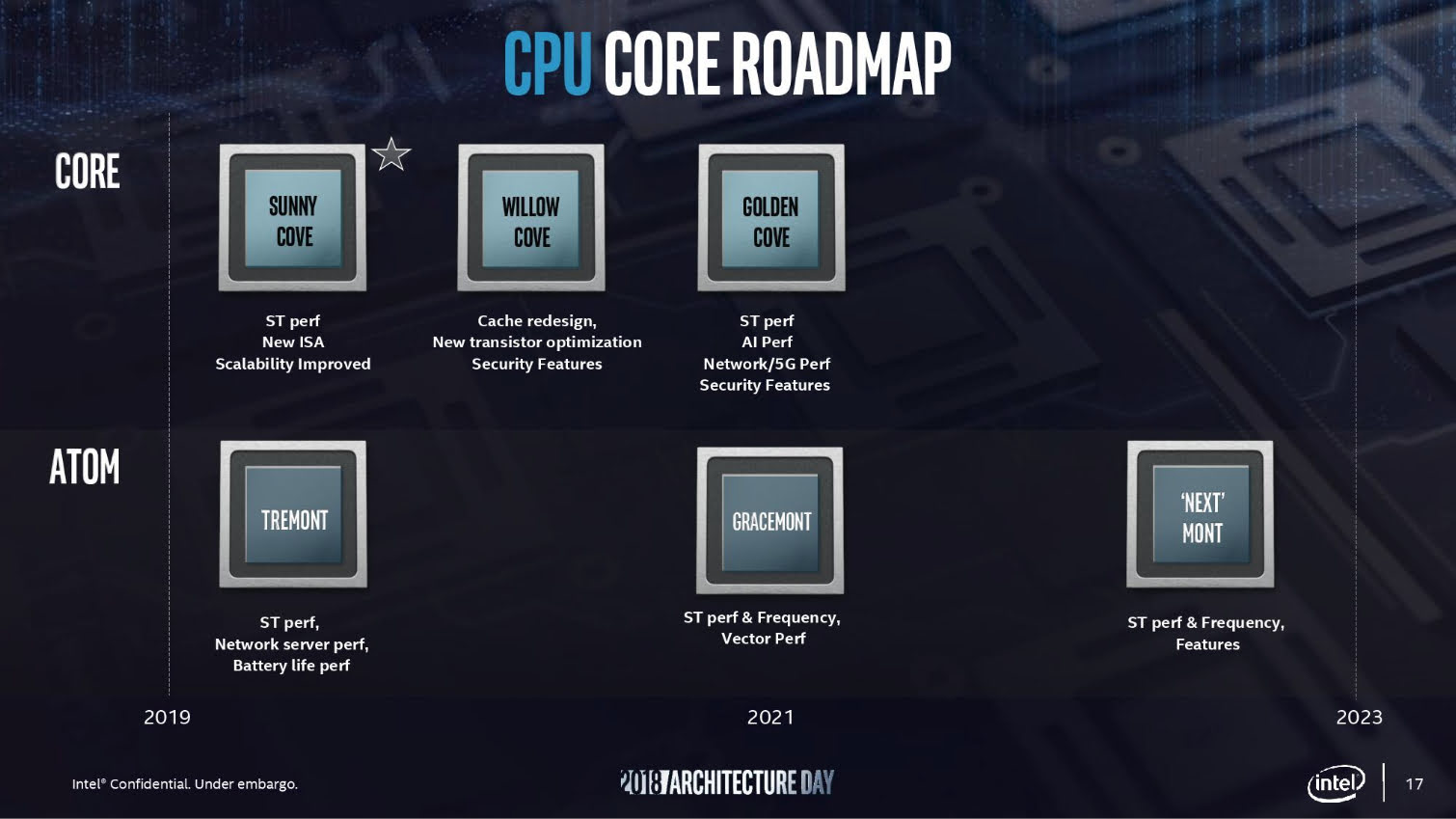

البته که مهمترین موضوع در این میان میزان حافظه کش سطح سه پردازنده چهار هستهای Tiger Lake U است که 12 مگابایت اعلام شده، یک افزایش 50 درصدی که یعنی هر هسته شامل 3 مگابایت حافظه کش سطح سه خواهد بود. چنین موضوعی ادعای اینتل مربوط به باز طراحی حافظه کش در معماری Willow Cove (هسته حاضر در Tiger Lake) را تایید میکند. اگر چه که باز طراحی حافظه کش باید بزرگتر از تنها افزایش حجم آن باشد. برای مثال حافظه کش بزرگتر دارای تاخیر بالاترییست، بنابراین باید شاهد بهینه سازیهای مختلفی در این بخش باشیم.

Tiger Lake قرار است در ماه آینده عرضه شود. یک بنچمارک از Tiger Lake لو رفته که نشان میدهد باید منتظر پردازندههای گرافیکی نسل دوازده Xe در آنها باشیم که شامل قابلیتهای نمایشی جدید و دستورالعملهای به روز شده میشود.

والا با چهار هسته ای و کش l3 با حجم ۱۲ مگابایت OH MY GOD یا OH MY LORD

خیلی فشار به این تایگر آوردین چاخان پزا

والا این BEE LAKE هم نیست چه برسه به تایگر لیک ووووواااااااااووووووووو WWWWWOOOOOOOOWWWWWWWWW

12 مگ الان خیلی خفنِ؟! این اینتل هم شوخیش گرفته…