افزایش كارایی از چه روشی؟

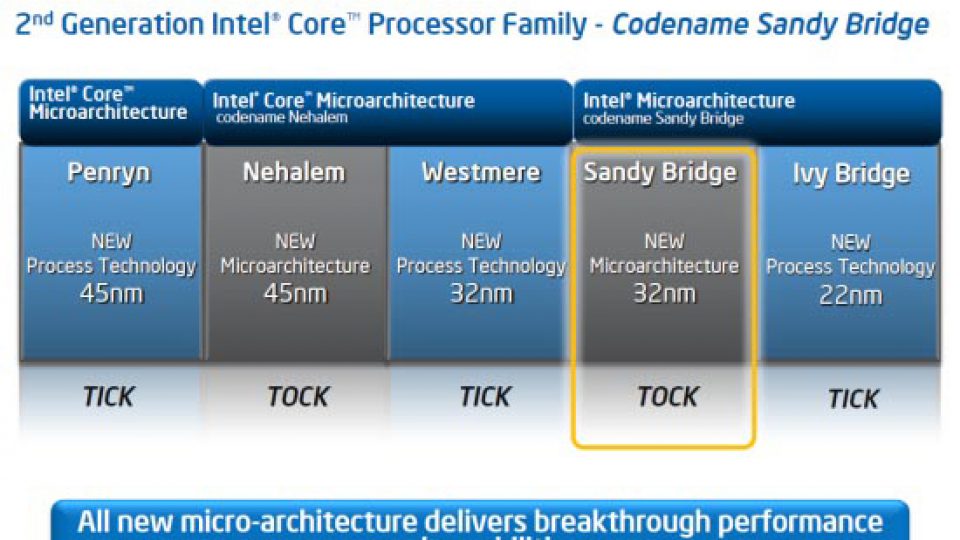

شركت اینتل در معماری Sandy Bridge چندین تغییر غیرمنتظره ایجاد كرده كه به موجب آن كارایی پردازنده افزایش و در مقابل مصرف توان و درجه حرارت آن كاهش پیدا كردهاست. در حقیقت، Sandy Bridge معماری توسعهیافته Nehalem نیست، بلكه این معماری تركیبی از معماری Nehalem با پروژه به ظاهر شكستخورده پنتیوم 4 است. بله؛ درست متوجه شدهاید، اگرچه معماری NetBurst شركت اینتل مدت زمان زیادی است كه به دلیل مصرف توان ناكارآمد منسوخ شده اما اكنون از برخی واحدهای پردازندههای پنتیوم 4 در پردازندههای Core i5 ،Core i3 و Core i7 جدید استفاده شدهاست. شاید شنیدن این نكته جالب باشد كه اینتل عنوان كرده، اقتباس برخی از بخشها از پنتیوم 4 فقط برای افزایش كارایی نبوده بلكه بیشتر برای كاهش مصرف توان بودهاست.

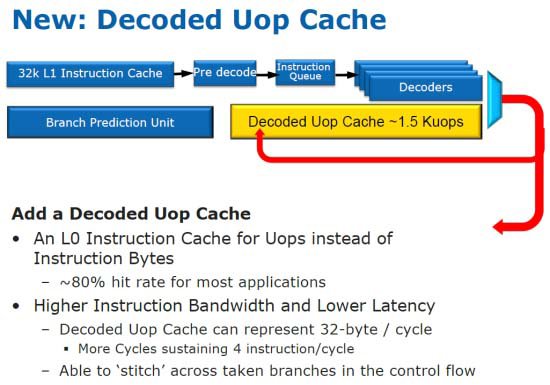

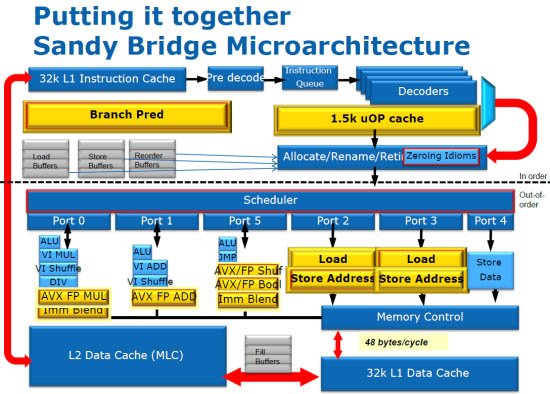

تغییرات انجامشده در معماری Sandy Bridge را با بررسی خط لولهها آغاز میكنیم. در ابتدای خط لولهها، رمزگشاها قرار دارند كه همچون گذشته دستورالعملهای x86 را به Micro-ops سادهتر رمزگشایی میكنند. رمزگشاها در معماری جدید مشابه با Nehalem در هر سیكل چهار دستورالعمل پردازش میكنند و مانند گذشته از فناوری Micro-Fusion و Macro Fusion نیز پشتیبانی میكنند. اما در معماری جدید، دستورالعملهای رمزگشاییشده به Micro-Opsها به جای اینکه به مرحله بعدی پردازش بروند، ذخیره میشوند. در حقیقت، Sandy Bridge یك حافظه سطح صفر اضافی برای ذخیره نتایج رمزگشایی دارد. این حافظه نهان اولین بخشی است كه از معماری NetBurst برگرفته شدهاست. عملكرد كلی این حافظه نهان مشابه Execution Trace Cache است كه در پردازندههای پنیتوم 4 بهكار گرفته شدهبود.

حافظه نهان Micro-Opsهای رمزگشاییشده حدود شش كیلوبایت است كه میتواند حداكثر یکهزار و پانصد Micro-Ops در خود ذخیره كند. اكنون اگر رمزگشا دستورالعملی دریافت كند كه قبلاً ترجمه كرده و در حافظه نهان نیز ذخیره شده، دوباره آن دستورالعمل را رمزگشایی نمیكند و از Micro-Ops مربوط به آن دستورالعمل كه در حافظه نهان Micro-Ops ذخیره شده، استفاده میكند. بنابراین حافظه نهان Micro Opsهای رمزگشاییشده به حذف بار اضافی از رمزگشاها كمك میكند و همچنین موجب كاهش مصرف انرزی پردازنده میشود. بنابر گفته مهندسان اینتل در هشتاد درصد مواقع دسترسی به این حافظه نهان اضافی موردنیاز است. گذشته از این، زمانی كه رمزگشاها در معماری Sandy Bridge بیكار هستند، غیرفعال میشوند كه این موضوع به كاهش مصرف توان پردازنده كمك میكند.

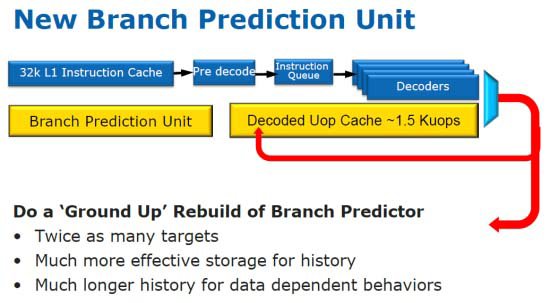

دومین پیشرفت مهم در خط لولهها مربوط به واحد پیشبینی انشعاب است. این واحد از اهمیت بسزایی در پردازندهها برخوردار است زیرا هر پیشبینی انشعاب نادرست نیازمند توقف و تخلیه خط لولهها بهطور كامل است. در نتیجه، یك پیشبینی اشتباه نه تنها روی كارایی اثر منفی دارد، بلكه موجب افزایش توان مصرفی برای پر كردن دوباره خط لوله میشود. اینتل به این واحد در پردازندههای جدید توجه ویژهای كرده تا آنها بهطور موثرتری عمل كنند. این شركت همه بافرهای Sandy Bridge را كه برای ذخیره آدرسهای انشعابها و تاریخچه پیشبینی بهكار گرفته شده، به منظور افزایش حجم ذخیرهسازی در آنها اصلاح كردهاست. در نتیجه Sandy Bridge اكنون قادر است تاریخچه پیشبینی انشعابهای طولانیتری ذخیره كند. این موضوع تأثیر زیادی روی كارایی واحد پیشبینی انشعاب میگذارد. مطابق برآوردهای اولیه، درستی پیشبینی انشعاب در Sandy Bridge به بیش از پنج درصد در مقایسه با نسل قبل بهبود پیدا كردهاست.

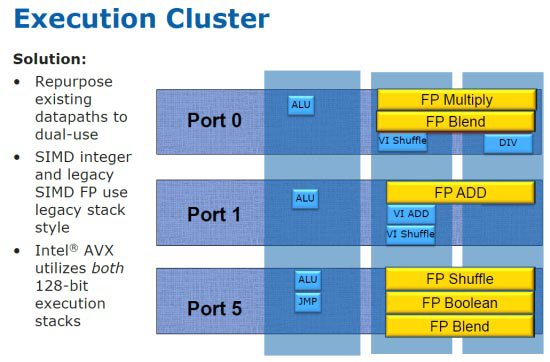

همانطور كه گفته شد، واحد پیشبینی انشعاب در پردازندههای غیرترتیبی از اهمیت بالایی برخوردار است و اغلب، سازندگان با معرفی یك معماری جدید تغییراتی در این واحد اعمال میكنند. این واحد در معماری Sandy Bridge از نظر ساختار شباهت بسیاری به معماری NetBrust دارد. مهندسان اینتل یكبار دیگر به عقب برگشته و از رجیستر فایل درون پردازنده جدید خود استفاده كردهاند (اگر به خاطر داشتهباشید، مهندسان اینتل این رجیستر فایلها را در پردازندههای Nehalem و Core بازنشسته كردند). در گذشته زمانیكه Micro-Opsها بازآرایی میشدند، كپی كاملی از رجیسترها برای هر عملیات در رجیستر فایلها ذخیره میشد. اما اكنون از مسیر (Link) به مقادیر رجیستری ذخیرهشده در یك رجیستر فایل استفاده میشود. این رویكرد علاوه بر اینكه موجب حذف انتقال دادههای مفرط میشود، از تكرار محتویات رجیستر نیز جلوگیری میكند و موجب ذخیره فضا در رجیستر فایل میشود. خوشه (Cluster) غیرترتیبی در پردازندههای Sandy Bridge میتواند در زمان یكسانی تا حداكثر 168 Micro-Ops نگه دارد، در حالیكه پردازندههای Nehalem قادر به ذخیرهسازی تنها 128 Micro-Ops در ROBهای خود (Reorder Buffer) بودند. این موضوع موجب كاهش مصرف انرژی میشود. به هر حال، جایگزین کردن روش مسیردهی به رجیستر فایلها در عوض دسترسی به مقادیر واقعی آنها اثرات منفی نیز به همراه دارد. این موضوع سبب شده تا مرحله جدیدی به خط لولههای اجرایی پردازنده اضافه میشود. پردازندههای مبتنی بر Sandy Bridge از دستورالعملهای AVX جدید با رجیسترهای 256 بیتی پشتیبانی میکنند. دستورالعملهای AVX در حقیقت جزئی از پیشرفت SSE به شمار میآیند که در آن اندازه رجیسترهای SIMD رأس به 256 بیتی افزایش یافتهاست. در نتیجه، مجموعه دستورالعملهای AVX، مشابه پیشرفت ریزمعماری، میتواند موجب افزایش کارایی و کاهش توان مصرفی شود. زیرا اجرای این دستورالعمل اجازه خواهد داد تا بسیاری از الگوریتمها ساده شده و از دستورالعملهای کمتری برای تکمیل وظایف استفاده شود. دستورالعملهای AVX برای محاسبات ممیز شناور سنگین در كاربردهای چندرسانهای، علمی و مالی کاملاً مناسب است. واحدهای اجرایی پردازنده برای اینكه بتوانند دستورالعملهای 256 بیتی را بهطور مؤثرتری اجرا كنند، باید دوباره طراحی میشدند. اینتل در طراحی جدید، دو واحد اجرایی 128 بیتی با یكدیگر جفت كرده تا بتوانند بستههای اطلاعات 256 بیتی را بهطور مؤثری پردازش كنند. از این رو، هر یك از سه پورت اجرایی در پردازندههای Sandy Bridge واحدهایی برای كار همزمان با سه نوع داده (64 بیت، 128 بیت عدد صحیح و 128 بیت عدد حقیقی) دارند. این موضوع موجب میشود، واحدهای SIMD با یكدیگر درون یك پورت یكسان جفت شوند.

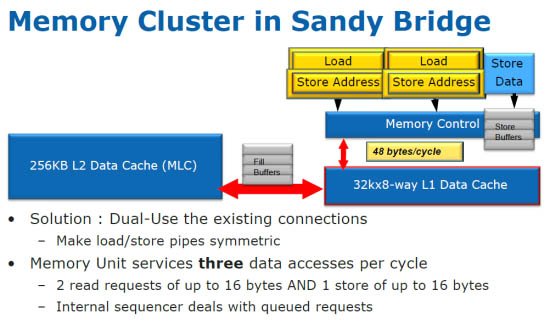

از آنجا كه Sandy Bridge برای كار با دستورالعملهای رأسی 256 بیتی طراحی شدهاست، اینتل باید به كارایی واحدهای اجرایی مسئول برای بارگذاری و تخلیه توجه ویژهای میكرد. در پردازندههای Nehalem سه پورت برای این منظور طراحی شدهبود كه اكنون نیز در Sandy Bridge این پورتها موجود هستند. اما به منظور افزایش بهرهوری این واحدها، مهندسان اینتل، دو واحد از این سه واحد را كه برای ذخیرهسازی آدرسها و بارگذاری اطلاعات استفاده میشد با یكدیگر ادغام كردهاند. اكنون این دو واحد عملكرد یكسانی دارند و هر یك میتوانند آدرسها و دادهها را بارگذاری یا آدرسها را تخلیه كنند. از این رو، هر پورت میتواند به واسطه عملكرد حداكثر شانزده بایت در هر سیكل، كل توان عملیاتی حافظه نهان سطح یك داده در معماری جدید را به میزان پنجاه درصد افزایش دهد. به عبارت دیگر، پردازندههای مبتنی بر معماری Sandy Bridge میتواند در هر سیكل 32 بایت داده از حافظه نهان سطح یك داده بارگذاری و شانزده بایت داده در آن ذخیره كنند.

اگر همه نوآوریهای شرح داده شده در بالا را در كنار یكدیگر قرار دهیم، خواهیم دید، معماری هستههای محاسباتی در پردازندههای Sandy Bridge بهطور چشمگیری اصلاح شدهاست. این تحولات آنقدر جدی هستند كه به سادگی بتوان گفت، پردازندههای جدید اینتل از یك معماری كاملاً متفاوت با پردازندههای Nehalem بهره میبرد.

رویكرد جدید به سمت یكپارچهسازی

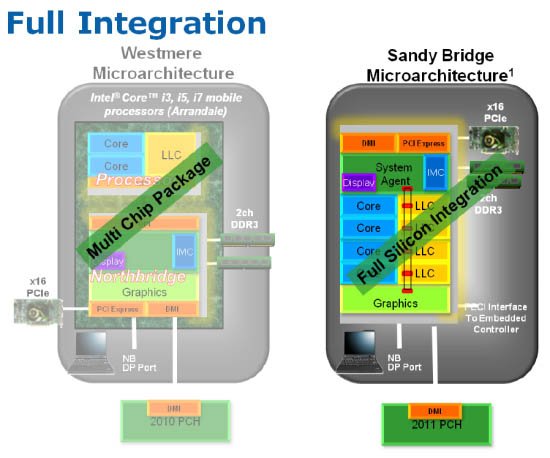

اینتل با معرفی معماری Nehalem شروع به گنجاندن اجزاء چیپست در پردازنده كرد. در معماری Nehalem كنترلر حافظه، كنترلر رابط PCI Express و پردازندهگرافیكی، درون پردازنده گنجاندهشد. به عبارت دیگر، با این تحولات، پردازندهها دیگر تنها یك واحد اجرایی مركزی نیستند، بلكه مجموعهای از واحدهای پیچیده مختلف هستند.

گنجاندن این واحدها درون پردازنده، موجب افزایش كارایی ناشی از كاهش زمان انتظار هنگام انتقال اطلاعات میشود. به هر حال، گنجاندن واحدهای مختلف در پردازنده مشكلاتی را نیز به همراه دارد. یكی از مهمترین موانع بر سر این راه، چگونگی اتصال این واحدها به یكدیگر به خصوص از نظر الكتریكی است. در این بین، اتصال حافظه نهان سطح سه اشتراكی با هستههای پردازندهها یكی از سختترین كارها برای سازندگان است، به خصوص اینكه تعداد هستهها روز به روز افزایش پیدا میكند. به عبارت دیگر، زمانی كه مهندسان اینتل در حال كار روی معماری پردازندههای Sandy Bridge بودند، باید برای اتصال مناسب بین همه واحدهای درون پردازنده فكر جدی میكردند. در معماری Nehalem و معماریهای ماقبل، از اتصال Crossbar عمومی استفاده شده اما این اتصال برای پردازندههایی با چندین واحد متفاوت مناسب نیست. مهندسان اینتل پیش از این در پردازندههای هشت هستهای سرور Nehalem-EX برای متصل كردن هستههای محاسباتی به حافظه نهان سطح سه از فناوری جدیدی استفاده كردهاند. این فناوری Ring Bus نام دارد و اینتل اكنون در معماری Sandy Bridge نیز از آن استفاده كردهاست. همه هستههای محاسباتی، حافظه نهان، پردازندهگرافیكی و عناصر پلجنوبی درون پردازنده جدید به باس حلقه (Ring Bus) متصل شدهاند كه اجازه میدهد تعداد اتصالات درون هسته به میزان قابل توجهی كاهش پیدا كند. مهندسان اینتل حافظه نهان سطح سه پردازندههای Sandy Bridge را به چهار بانك یكسان تقسیم كردهاند كه هر بانك دو مگابایت ظرفیت دارد. به عبارتی، تعداد این بانكها دقیقاً یكسان با تعداد هستههای پردازنده است. این استراتژی اینتل به نظر میرسد بیشتر برای بازاریابی بود زیرا اینتل با جدا كردن این بانكها میتواند پردازندههایی با حافظههای نهان متفاوت و قیمتهای مختلف تولید كند. بهطور مثال، پردازندهای ارزانقیمت با شش مگابایت حافظه نهان سطح سه به جای هشت مگابایت تولید كند. هر یك از بانكهای حافظه نهان توسط «arbiter» خودشان اداره میشوند اما در زمان یكسان همه آنها مشابه با یكدیگر كار میكنند و دادهها در آنها هرگز تكراری نخواهدبود. استفاده از این بانكها، موجب تقسیم حافظه نهان سطح سه نمیشود، بلكه تنها پهنای باند حافظه نهان سطح سه را افزایش میدهد. برای مثال، از آنجا كه «Ring» عرض 32 بیتی دارد، حداكثر پهنای باند حافظه نهان سطح سه درون یك پردازنده چهارهستهای كه در فركانس 3/4 گیگاهرتز عمل میكند، برابر با 435/2 گیگابایت در ثانیه است. اینتل با این روش، به سادگی میتواند با افزایش تعداد هستههای پردازنده، تعداد بانكهای حافظه نهان سطح سه را نیز افزایش دهد.

از دیگر مزایای حافظه نهان سطح سه جدید میتوان به كاهش زمان تأخیر آن اشاره كرد. اكنون زمان تأخیر حافظه نهان سطح سه بین 26 تا 31 سیكل است. این زمان در حافظه نهان سطح سه پردازندههای Nehalem بین 35 تا 40 سیكل بود. این توضیح لازم است كه تمامی حافظههای نهان در پردازندههای Sandy Bridge با فركانس پردازنده كار میكنند. به هر حال، این موضوع نیز سبب شده تا عملكرد حافظه نهان در این پردازندهها سریعتر شود. برتری دیگر باس حلقه این است كه از آن برای انتقال اطلاعات دادههای مربوط به پردازندهگرافیكی كه درون پردازنده گنجانده شدهاست نیز استفاده میشود. این یعنی، پردازندهگرافیكی درون پردازنده، بهطور مستقیم با حافظه در ارتباط نیست. این واحد شبیه هسته پردازنده با حافظه نهان سطح سه در ارتباط است. این موضوع سبب میشود، كارایی پردازندهگرافیكی بهطور چشمگیری افزایش پیدا كند.

دیدگاهتان را بنویسید