دکتر مارک لیو، رئیس شرکت معظم تولید نیمه هادی تایوان (TSMC) در کنفرانسی، برنامه تولید فناوری ۳ نانومتری شرکت TSMC رونمایی کرد. TSMC (شرکت تولیدکننده مادر که پردازندهها را به مشتریان در سراسر جهان میرساند) در حال حاضر در حال ساخت تسهیلات تولید تراشههای 3 نانومتری است و امیدوار است که تولید این محصولات را از سال آینده آغاز کند.

جزئیات برنامه تولید فناوری ۳ نانومتری شرکت TSMC

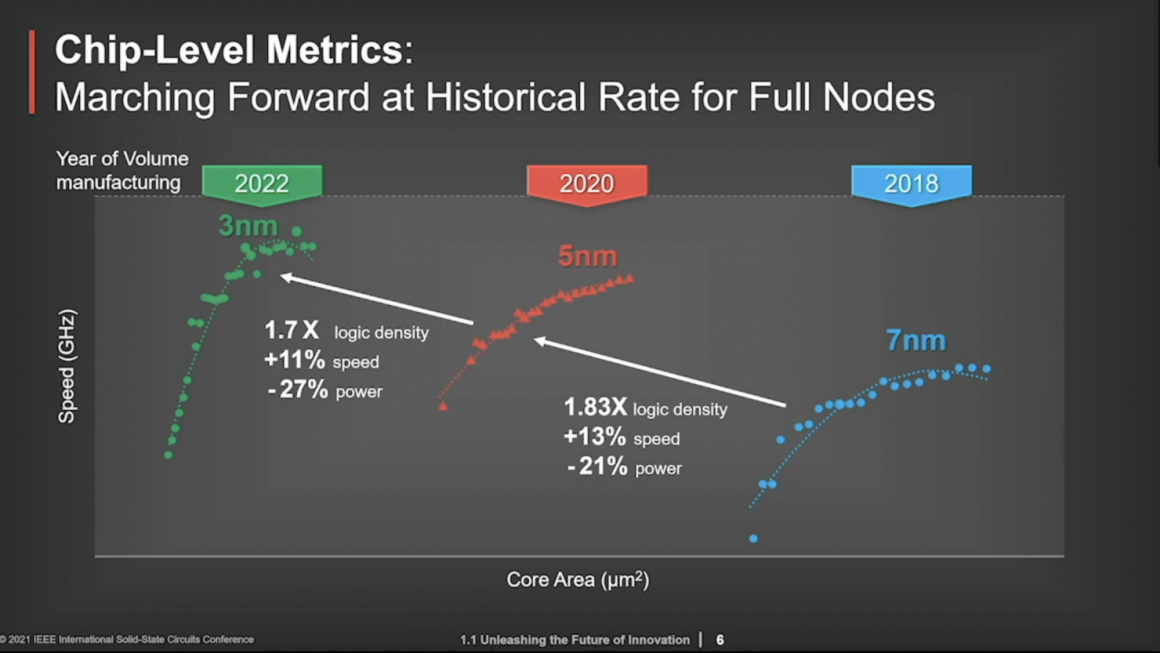

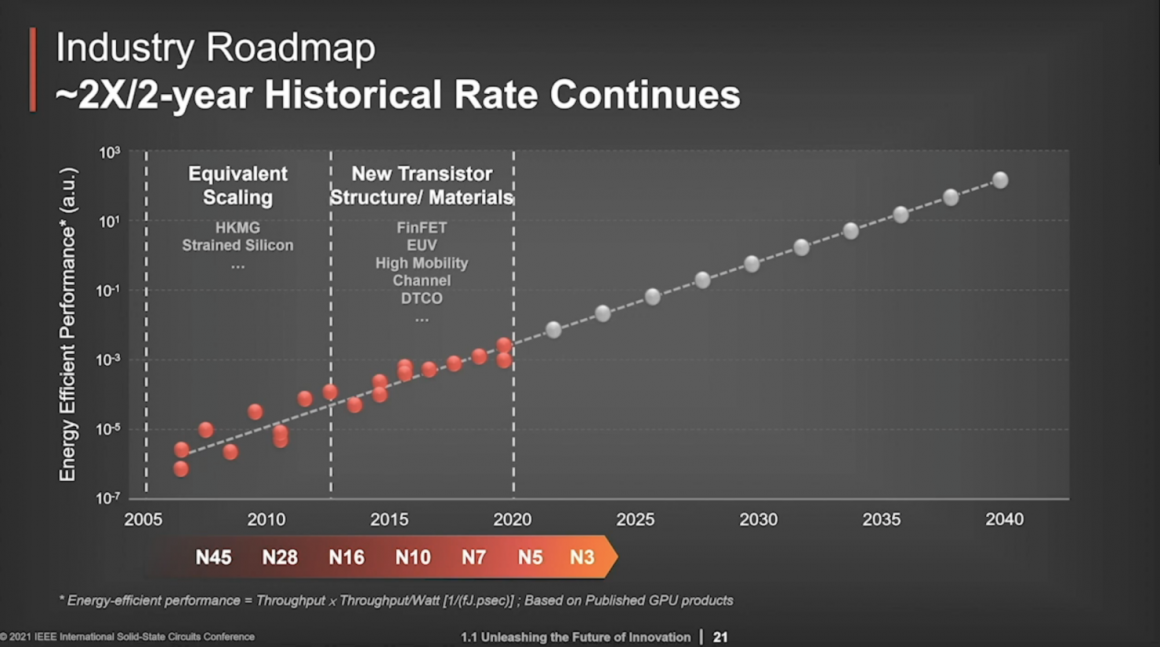

فناوری 3 نانومتر TSMC تقریباً دو برابر تراکم منطقی نسبت به فناوری 5 نانومتری خواهد داشت و در پی آن 11٪ افزایش عملکرد یا 27٪ بهره وری انرژی را به همراه خواهد داشت. نظرات مدیر اجرایی این شرکت در مورد فناوری تولید بعدی شرکت نشان دهنده این است که TSMC قادر خواهد بود هم افزایش تقاضا برای محصولات فعلی و هم محصولات آتی خود را به صورت همزمان مدیریت کند. همه اینها در شرایطی است که به شرکتهای دیگر هم اجازه نمیدهد تا تقاضای اخیر محصولات خود بر تولید آن تأثیر بگذارد. برنامه تولید تراشه ۳ نانومتری در هنگام سخنرانی وی در کنفرانس بین المللی مدارهای حالت جامد (ISSCC) با عنوان “آزادسازی آینده نوآوری” که روز دوشنبه هفته گذشته برگزار شد، معرفی شد.

دکتر لیو جدای (مدیر اجرایی تراشه ۳ نانومتری) با بیان اینکه “طرح توسعه فناوری 3 نانومتری پیشرفت خوبی داشته و برنامه ما به خوبی پیش میرود”، آخرین ارقام مربوط به روند تولید تراشه 3 نانومتری و افکار خود در مورد وضعیت فعلی توسعه این فرآیند را ارائه داد. وی همچنین تأکید کرد که تا به امروز، شرکت TSMC تقریباً 1.8 میلیارد تراشه تولید شده با فرآیند 7 نانومتری شرکت را عرضه کرده است. این تراشهها تا سال گذشته در بالای زنجیره غذایی فرآیند شرکت قرار داشتند. به گفته وی، لیتوگرافی فوق العاده ماورابنفش(EUV) شرکت TSMC را قادر ساخته است تا زمان چرخه کوتاهتر و کاهش پیچیدگی فرآیند و نرخ نقص را بدست بیاورد. بعلاوه، طبق گفته دکتر لیو، شرکت او از EUV در با 10 لایه پوششی برای تولید فناوری 5 نانومتری در برش خط، الگوی تماس و خط فلزی استفاده میشود.

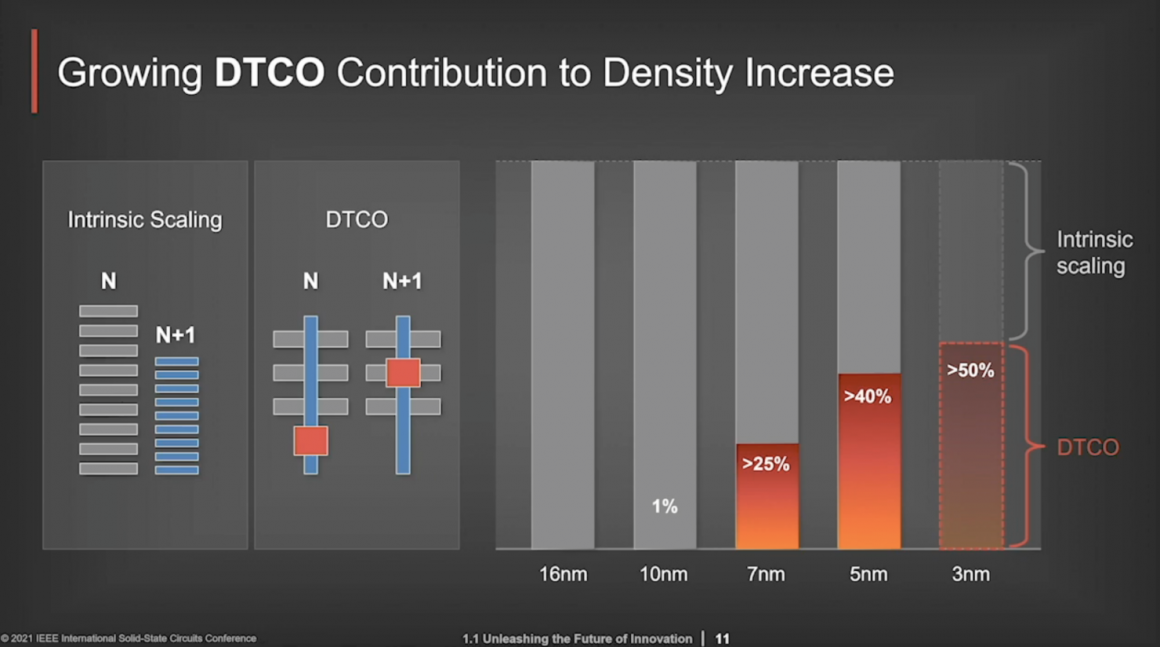

پس از اینها رئیس TSMC ادامه داد كه چگونه بهینه سازی طراحی فناوری (DTCO) در طی چند سال گذشته برای تولید تراشه از اهمیت بیشتری برخوردار شده است. DTCO (که به تولیدکنندگان تراشه اجازه میدهد تا از فناوریهای طراحی و ساخت برای مطابقت با الزامات عملکرد استفاده کنند) TSMC را قادر ساخته است تا هنگام اندازه گیری تراکم منطقی یک گره، فراتر از معیارهای مقیاس گذاری ذاتی مانند گیت تماس و حداقل گام فلز حرکت کند. در عوض، به دنبال طراحی فناوری DTCO، ویژگیهایی مانند تماس با دروازه در منطقه فعال، وقفههای نفوذی تک و fin-depopulation برای ارائه تراکم منطقی 1.8X برای تراشه 3nm به کار گرفته شده است.

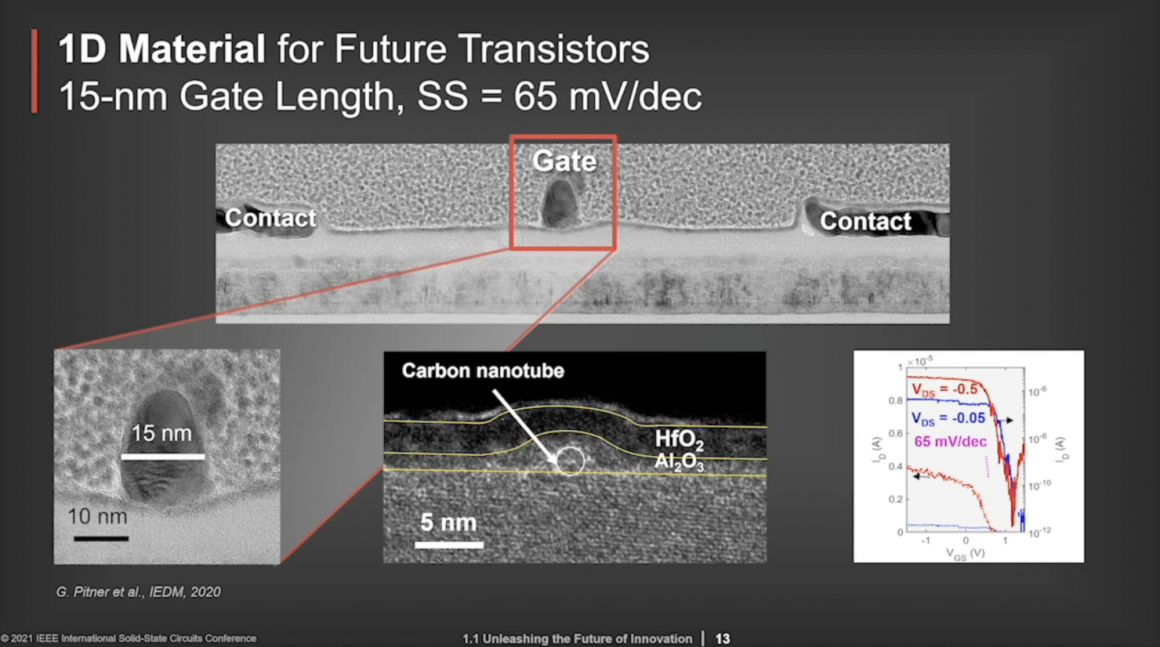

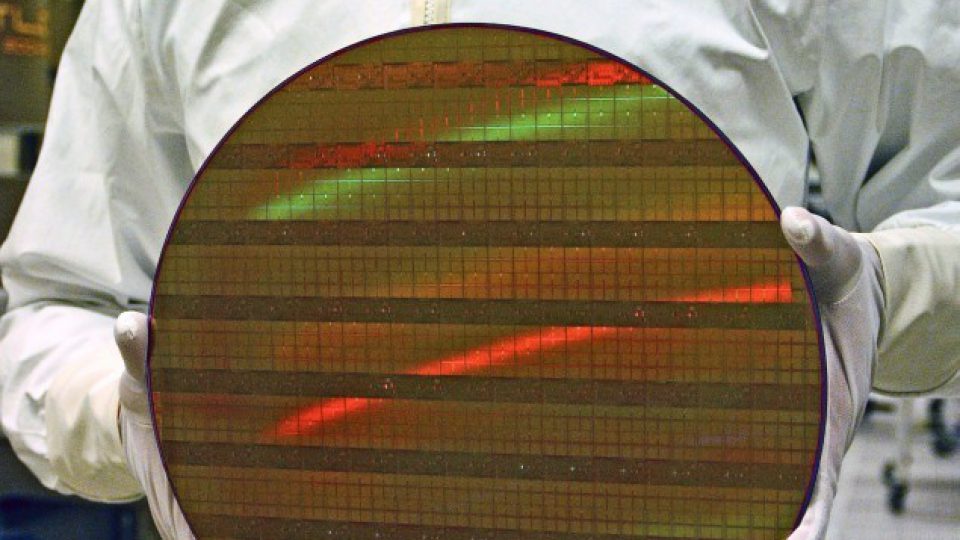

وی در انتها برنامههای شرکت خود را برای آینده اعلام کرد که شامل توسعه مواد 2 بعدی مانند رشد یک بور نیترید شش ضلعی تک بلور در مقیاس ویفر میشود. این کانال و مواد آن میتوانند در دمای پایین ساخت به لایههای دلخواه منتقل شوند که به گفته مدیر اجرایی، با انجام این کار راههایی برای ساخت لایههای منطقی و حافظه فعال در سه بعد باز میشود.

دیدگاهتان را بنویسید