اینتل با Panther Lake قصد دارد از طریق ادغام کنترلر حافظه (IMC) و دای محاسباتی، مشکلات تأخیر در معماریهای فعلی و اتصالات Die-to-Die (D2D) را بهبود دهد. این تغییر ممکن است در نسل بعدی، Nova Lake، دوباره به شکل نسلهای قبلی بازگردد. یکپارچه سازی کنترلر حافظه در معماری Panther Lake میتواند تاثیر زیادی در عملکرد پردازندههای نسل جدید این شرکت داشته باشد.

براساس اطلاعات افشاشده از منابع معتبر kopite7kimi و Jaykihn، اینتل با قرار دادن IMC و دای محاسباتی در یک قالب، به دنبال حل مشکلات عملکرد و کارایی است که در نسلهایی مانند Arrow Lake وجود داشتهاند. این تصمیم به عنوان یک حرکت آزمایشی تلقی میشود.

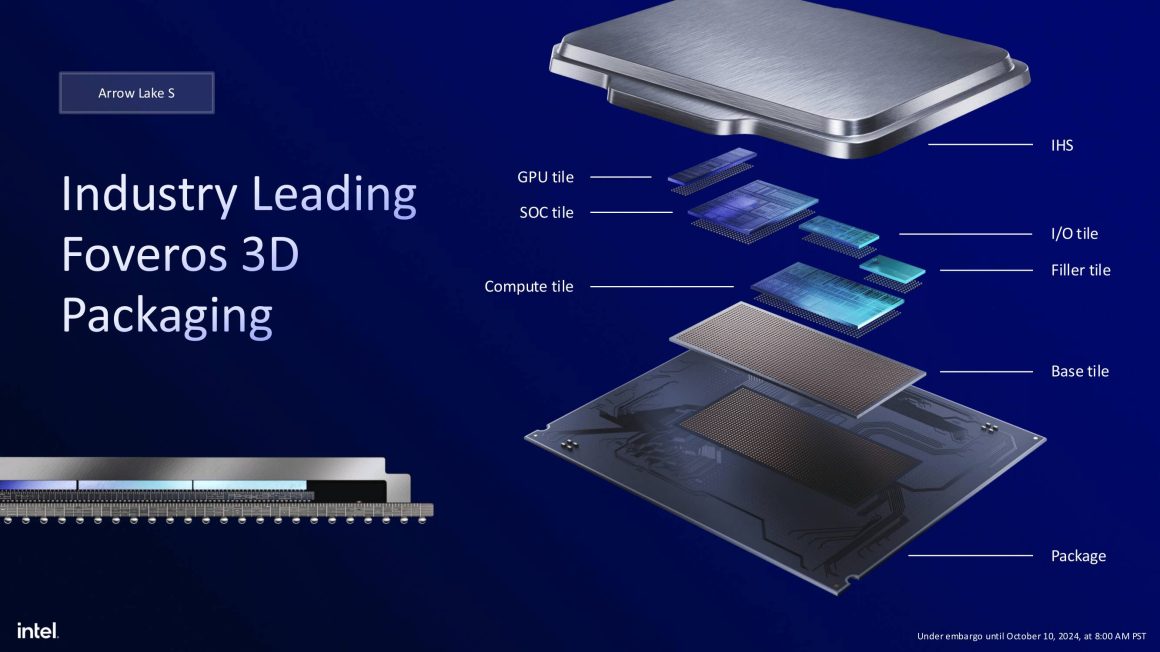

در معماری Arrow Lake، شکل IMC و دای محاسباتی جدا هستند و IMC در خارج از دای اصلی قرار گرفته است. این جداسازی باعث شده انتقال دادهها به دلیل عبور از اتصالات D2D، ناکارآمد و با تأخیر بیشتر انجام شود. با ادغام IMC در دای محاسباتی، تأخیر کاهش مییابد، زیرا دیگر نیازی به عبور دادهها از این اتصالات نیست و پردازش بهصورت مستقیم صورت میگیرد.

در صورت ادغام IMC در دای محاسباتی، اینتل ممکن است بخشهایی از معماری پردازنده را در Panther Lake حذف کند تا طراحی سادهتر و مقیاسپذیرتر شود و به اهداف عملکردی مدنظر برسد؛ به همین دلیل، این تغییر در معماریهای موجود مثل Arrow Lake اعمال نشده است.

زیرسیستمهایی که بهطور سنتی در یک کاشی SoC جداگانه قرار دارند، در Panther Lake به بخش محاسباتی منتقل شدهاند، زیرا بخشهای پردازنده اختصاصی در این طراحی وجود ندارد. عدم وجود بخش پردازنده اختصاصی به دلیل محدودیتهای مقیاس است.

— Jaykihn (@jaykihn0) 26 اکتبر 2024

به طور کلی، Panther Lake تغییرات طراحی مهمی را ارائه خواهد داد، اما نکته جالب این است که این تغییرات احتمالاً در Nova Lake به ساختار قبلی بازخواهند گشت، چرا که SoC tile در آن بازگشته و ارتقاءهای جدیدی در اتصالات D2D اعمال میشود. این رویکرد “آزمایش و خطا” نشان از تلاش اینتل برای بهبود اتصالات D2D و رقابت با فناوریهایی مثل Infinity Fabric در AMD دارد.

شایان ذکر است که همه این اطلاعات در حد شایعه هستند و اینتل هنوز به طور رسمی چیزی اعلام نکرده است، اما با توجه به عملکرد ناامیدکننده ARL، احتمالاً اینتل به دنبال تغییرات جدی خواهد بود.

مطالب مرتبط:

دیدگاهتان را بنویسید